# InP/GaAsSb DHBTs: THz Analog Performance and Record 180-Gb/s 5.5V<sub>ppd</sub>-Swing PAM-4 DAC-Driver (Invited)

C.R. Bolognesi<sup>1</sup>, A.M. Arabhavi<sup>1</sup>, R. Hersent<sup>3</sup>, S. Hamzeloui<sup>1</sup>, F. Jorge<sup>3</sup>, X. Wen,<sup>2</sup> M. Riet<sup>3</sup>, M. Luisier<sup>2</sup>, V. Nodjiadjim<sup>3</sup>, F. Ciabattini<sup>1</sup>, C. Mismer<sup>3</sup>, O. Ostinelli<sup>1</sup>, and A. Konczykowska<sup>3,4</sup>

1 Millimeter-Wave Electronics Group (MWE), ETH-Zürich

2 Integrated Systems Laboratory (IIS), ETH-Zürich

3 III-V Lab, joint lab: Nokia Bell Labs, Thales Research and Technology and CEA-LETI, France

4 ADesign, l'Haÿ-les-Roses, France

Abstract—"Type-II" InP/GaAsSb DHBTs are the first non-GaInAs -based transistors to show oscillation frequencies > 1 THz with the associated benefits of higher breakdown voltages, low power dissipation, and superior linearity and scaling characteristics. Whereas no large-signal characterization of THz transistors is found in the literature, THz InP/GaAsSb DHBTs display attractive 94 GHz load-pull characteristics, and less aggressively scaled devices achieve record saturated output power and output power density per unit emitter area. The physical advantages of Type-II InP/GaAsSb are reviewed here. Beyond impressive analog small/large-signal performance metrics, we report a record mixed-signal performance for a PAM-4 DACdriver designed and fabricated at III-V Lab in a 0.7-µm InP/GaAsSb DHBT technology implemented on epitaxial layers grown at ETHZ. The DAC-driver offers an unprecedented 5.5-Vppd 90-GBd (180 Gb/s) differential output swing with high eye diagram quality and over 12-dB gain control capability at a 1.1-W power consumption, leading to a record 3.1-GBd E/O modulator driver figure-of-merit (FoM). PAM-4 operation at 112-Gb (224 Gb/s) is also demonstrated with 3.35-Vppd and 0.6-W dissipation, also with a record 2.6-GBb E/O FoM. A 110 GHz bandwidth linear driver with a 16.7 dB gain and 0.85-W consumption was also implemented in the same technology, enabling a 4.1-Vppd output swing at 100 Gb/s both in PAM-4 and NRZ signaling. The allaround outstanding performance of InP/GaAsSb DHBTs makes them attractive for a wide variety of analog and mixed-signal circuit blocks used in modern telecommunication applications.

Keywords—Type-II DHBTs, InP/GaAsSb, Power Amplifiers (PAs), Pulse-Amplitude Modulation Format (PAM-4), Linear Driver, Analog/Digital Circuits

## I. INTRODUCTION

"Type-II" double heterojunction bipolar transistors (DHBTs) based on the InP-Ga(In)AsSb material system provide the highest available  $f_{\rm T} \times BV_{\rm CEO}$  and  $f_{\rm MAX} \times BV_{\rm CEO}$  products, as well as the highest reported  $f_{\rm MAX}$  for a bipolar transistor [1]. Quaternary InP/GaInAsSb DHBTs also enabled the highest transistor  $f_{\rm T}$  ever reported [2]. With a colleague from SFU, the first author secured a modest Canadian NSERC grant targeting the development of 150 GHz transistors in 1996 [3], and initiated InP/GaAsSb DHBT work with the epitaxy InP-

GaAsSb heterostructures and the measurement of their band alignment [4]. With a remarkably fast "lab-to-fab" transition, GaAsSb-based DHBTs went into industrial production in 2004/5, following the transfer of a basic process from our Group to HP Labs (Palo Alto, CA) in 2001. Over the last 25 years, InP/GaAsSb DHBTs evolved from (75 × 75) μm<sup>2</sup> devices to the first non GaInAs-based transistors with  $f_{\text{MAX}} > 1 \text{ THz}$ , and the *only* THz transistor to be organically developed, from DC to THz bandwidths, entirely within one group (first at SFU, and since 2006 at ETHZ). This unique development thread is even more surprising in that it was largely achieved by small teams of Ph.D. students and few postdoctoral fellows (pre-2008: 1 on epitaxy, 2 on device technology), with an infinitesimal fraction of the funding distributed by various agencies for THz technology InP/GaAsSb DHBTs were perhaps simply meant to be. GaAsSb application to DHBTs now appears in the SRC 2020-2030 Decadal Plan [5], without reference to the field (though the Plan mentions "recent runs" show the resistance of GaAsSb to H2 passivation in MOCVD-grown layers, a finding first reported in 1996 [6], and later confirmed in [7]). While on the topic of crediting prior art, it must be noted that the first InP/GaAsSb DHBTs were independently demonstrated by workers from Rockwell [6] and Bellcore [8] in 1996: initial results did not appear promising, and GaAsSb activities were promptly terminated. Interestingly, the only early industrial adopters of InP/GaAsSb technology (Agilent, and the defunct Nortel) did not have existing InP/GaInAs SHBT processes: they initiated InP/GaInAs and InP/GaAsSb DHBT development in parallel. Both organizations sped internal developments up by proofing their home-grown material with high-speed InP/GaAsSb DHBTs fabricated in the author's group, before fabricating their own devices [9, 10]. It paid off: already with early insertion by the mid-2000's, improved yields increased profits by \$10k per T&M instrument sold by the former company [11].

In late 2021, the ETH-MWE Group demonstrated a new emitter fin process allowing the arbitrary tuning of the base access distance and yielding a record  $f_{\text{MAX}} = 1.2 \text{ THz}$  in  $(0.25 \times 4.4) \, \mu\text{m}^2 \, \text{InP/GaAsSb DHBTs}$  [1]. The devices offer an

SNF/ANR ULTIMATE (200021L\_169413).

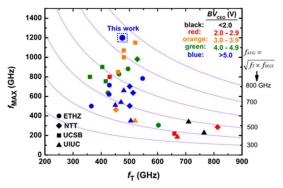

$f_{\text{MAX}} \times BV_{\text{CEO}} = 6.48 \text{ THz-V}$ , the highest ever reported in any transistor. A clear breakthrough in device scaling, 9.4-µm-long devices also achieve  $f_{\text{MAX}} > 1$  THz with an emitter area of 1.645 µm<sup>2</sup>. In comparison, the previous InP DHBT state-of-theart reported  $f_{\text{MAX}} = 1.15 \text{ THz}$  with  $BV_{\text{CEO}} = 3.5 \text{ V}$  and a 0.26 µm<sup>2</sup> emitter area [12]. The scaling and breakdown advantages of InP/GaAsSb technology are obvious. Further perspective is gained by defining  $f_{\text{AVG}} = (f_{\text{T}} \times f_{\text{MAX}})^{1/2}$  as a figureof-merit of balanced performance. This leads to a record InP DHBT metric of  $f_{AVG} \times BV_{CEO} > 4$  THz-V, approaching the 4.49 THz-V of 20-nm GaN HEMTs [13] (reaching 4.9 THz-V with a less stringent  $BV_{\text{CEO}}$  defined at  $J_{\text{C}} = 10 \,\text{kA/cm}^2$ ). InP/GaAsSb DHBTs also compare well to the highest reported InP HEMT performance with  $f_T/f_{MAX} = 0.61/1.5$  THz and  $BV_{DS} = 3 \text{ V}$ , with a corresponding  $f_{MAX} \times BV_{DS} = 4.5 \text{ THz-V}$ and  $f_{\text{AVG}} \times BV_{\text{DS}} < 2.9 \text{ THz-V}$  [14]. Despite a long list of favorable device metrics, the InP/GaAsSb DHBT literature remains sparse in terms of their use in circuits (with few exceptions [15-16], including a record efficiency 0.5 THz oscillator [16]). We partly remedy this situation below with leading edge high-performance circuit demonstrations.

This paper is organized as follows: Section II outlines unique device operation advantages of InP/GaAsSb DHBTs. Section III shows properties of InP/GaAsSb DHBTs pertinent to analog power amplifiers (PAs) operating at mm- and sub-mm-wave frequencies. Section IV describes a 0.7-µm technology developed at III-V Lab on ETHZ epilayers, and its application to record-setting high-symbol-rate large-output-swing integrated circuits (ICs).

# II. INP/GAASSB TYPE-II DHBTS

# A. Band Diagram and Device Operation

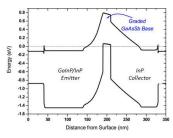

Fig. 1 shows the equilibrium band diagram of a graded-base InP/GaAsSb DHBT. A composite InP emitter with a graded GaInP layer results in  $\Delta E_{\rm C} = 0$  eV at the E/B junction: this favors thermal injection of electrons into the base and leads to a collector current ideality factor  $n_{\rm C} = 1.0$ , increases gain and ensures the sharpest device turn-on while contributing to a low-power dissipation. Turn-on voltages are lower than in Silicon BJTs (because the GaAsSb energy gap is only ~0.72 eV).

Fig. 1. Equilibrium band diagram of a graded-base InP/GaAsSb DHBT. The GaAsSb base uses compositional and C-doping gradings. Note the rather unusual mixed-group V grading, an innovation introduced by the ETH-MWE. Also note  $\Delta E_{\rm C}=0$  eV at the E/B junction, and the large  $\Delta E_{\rm V}$  at both junctions.

The "Type-II" band alignment between InP and GaAsSb allows the use of an abrupt heterojunction at the base-collector interface with a binary InP collector. This inherently provides several advantages: InP shows high peak and saturated drift

velocities for electrons, high breakdown fields, as well as a much higher thermal conductivity than GaInAs/AlInAs layers. The InP/GaAsSb band line-up allows electron collection in InP down  $V_{\rm CB} < 0$  V, permitting excellent device performance down to low  $V_{\rm CE}$ , an advantage for low-power dissipation and large signal swing applications. Furthermore, InP enables selective wet etching of the collector and sub-collector layers during fabrication, a manufacturing advantage [11] at least as significant as GaInP emitters were for GaAs HBTs.

The sizable valence band discontinuity  $\Delta E_{\rm V}$  at the E/B and B/C junctions not only eliminates hole back-injection into the emitter, but it also suppresses the base pushout experienced in homojunction collectors at high collector current densities and low  $V_{\rm CE}$ . To some extent, base pushout also takes place in InP/GaInAs DHBTs using a GaInAs spacer between the base and the collector grading layer. As pointed out by others [17], the base-pushout saturation charge storage degrades transistor performance in analog and mixed-signal applications which cause the B/C junction to become forward-biased (particularly in switching-mode PAs which drive bipolar transistors between cutoff and saturation [17], but also in conventional PAs and digital circuits). As shown in Section IV, InP/GaAsSb DHBTs indeed provide outstanding mixed-signal circuit performance.

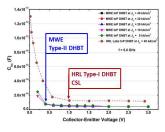

Fig. 2.  $C_{\rm BC}$  variation at 5 GHz in InP/GaAsSb and InP/GaInAs with a CSL-graded collector for relatively low  $J_{\rm C}$ . In contrast to GaInAs, the Type-II DHBTs show little variation untill  $V_{\rm CE}$  < 0.5 V. GaInAs data from [18].

Fig. 3. Zampardi-style [18] 28/40 GHz RF knee measurements for the devices of Fig. 2. Type-II devices show better gain stability  $vs.\ V_{\rm CE}$  (and hence overall RF linearity). The InP/GaAsSb DHBT advantage grows at higher frequencies.

Fig. 4. (a) OIP3 and  $G_P$  of InP/GaAsSb DHBTs with (a) different emitter widths and (b) different emitter lengths as a function of center frequency. IMD measurements were taken with a 4 MHz tone spacing and a 50  $\Omega$  load. Devices were biased for best  $f_T/f_{MAX}$ . OIP3 degrades by 1-2 dB between 10 and 40 GHz.

High-current low-voltage effects in the collector region of bipolar transistors also lead to variations of the collector-base feedback capacitance  $C_{BC}$  —Zampardi et al. showed the  $C_{BC}$ variation at low  $V_{\rm CE}$  is the major contributor to HBT nonlinearity [18]. One expects that a Type-I discontinuity in the B/C region exacerbates this effect when the bands flatten due to the electron space charge at high  $J_{\rm C}$  and low  $V_{\rm CE}$ , with the added complication of the previously discussed base pushout [14]. Indeed, UIUC workers first compared the linearity of InP/GaAsSb DHBTs and InP/GaInAs DHBTs with a chirped superlattice (CSL) collector, and found the former to offer better linearity at 18 GHz [19]. More recently, Bolognesi et al. reported the superior linearity of "Type-II" InP/GaAsSb DHBTs (with  $f_T/f_{MAX} = 480/640$  GHz and  $BV_{CEO} = 5V$ ) with respect to "Type-I" InP/GaInAs DHBTs, GaAs, and SiGe HBTs at low collector current levels [20]. Fig. 4 shows OIP3 and gain data vs. frequency for InP/GaAsSb DHBTs. OIP3 and GP load-pull contours of InP/GaAsSb DHBTs show that the high linearity and gain domains overlap well in the Smith chart. The OIP3 vs. J<sub>C</sub> curves of InP/GaAsSb DHBTs at 40 GHz show values similar to those of CSL-graded InP/GaInAs DHBTs  $(f_{\text{MAX}} = 650 \text{ GHz})$  measured at 10 GHz [21]. Recent ETHZ-MWE work to be reported elsewhere shows the linearity of InP/GaAsSb DHBTs is maintained at bias conditions needed for class-A and AB PA operation.

## B. InP DHBT Collector Transport Comparison

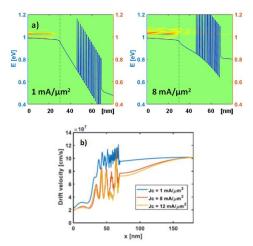

Fig. 5. Quantum-transport (QT) simulation of a chirp-superlattice graded InP/GaInAs DHBT. (a) band profile at low- and high- $J_C$ : red indicates a high current density, green no current. (b) electron velocity profile.

Because transistor linearity is a key consideration for PAs and modulator drivers used with higher-order modulation formats in high-capacity modern telecom systems, it is worth examining the effect of collector structures on transport to understand how their respective limitations arise. The following results are based on a ballistic 1-D full-band, atomistic quantum transport (QT) solver [22]: whereas commercial TCAD tools (such as used in [19]) rely on classical drift-diffusion (DD) or hydrodynamic (HD) models, without precise descriptions of energy band structures (*i.e.* Γ, L, and X-valleys), transient, or quantum mechanical phenomena (*e.g.* tunnelling), the following

simulations offer the most physical treatment of DHBT collector transport to date. First consider an InP/GaInAs DHBT with a CSL grading: Fig. 5a) shows the collector region band diagram for low and high collector current densities, while Fig. 5b) shows the corresponding computed electron velocity through the collector. It is clear that transport is severely perturbed at high- $J_{\rm C}$  due to tunnelling suppression. High- $J_{\rm C}$  charge storage effects are also evidenced by a reduced velocity in the base. This illustrates that graded interfaces that work well for some transistor bias are achievable, but that it is nearly impossible to realize a grading that performs well over a wide range of biases. In other words, for a given grading design (CSL or other), a bias exists for optimal transport. Large-signal operation however induces large current/voltage swings which result in nonoptimal collector transport over significant portions of the swing. Fig. 6 provides a similar simulation for a "Type-II" InP/GaAsSb DHBT: high-current effects decrease performance by field-reversal at high- $J_{\rm C}$ , but the impact on collector velocity is far weaker: there is little perturbation of transport in the collector, and nearly none in the base. This accounts for the weaker  $C_{\rm BC}$  modulation experienced in "Type-II" DHBTs at low  $V_{\rm CE}$ , as well as their superior linearity.

Fig. 6. (QT) simulation of an InP/GaAsSb DHBT: high- $J_{\rm C}$  conditions only marginally affect electron transport in the InP collector (right).

## III. INP/GAASSB DHBTs RF PROPERTIES

## A. THz DHBT Small-Signal Performance

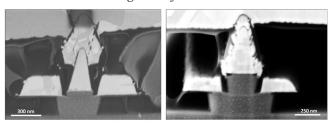

Fig. 7. Left: SEM image of an emitter fin InP/GaAsSb DHBT with a width of 250 nm and a 35 nm E/B access distance. The fin process allows much thinner semiconductor emitters compared to the standard process (right). From [1].

The recent ETHZ-MWE emitter-fin DHBT process enables: i) a tunable base-emitter access distance down to 10 nm, ii) the use of thick base contact metals (up to ~300 nm), and iii) the minimization of parasitic capacitances and resistances via precise lateral wet etching of the base-collector (B/C) mesa [1]. The process was demonstrated on a 20-nm GaAs<sub>x</sub>Sb<sub>1-x</sub> base, implemented with the As-mole fraction ramped from x = 0.59 at the emitter to x = 0.41 at the collector interface. The base layer also uses a linear grading of the carbon p-doping with an average level of  $8.5 \times 10^{19}$  cm<sup>-3</sup>. The overall structure used a thinner 20 nm n+ InP emitter and 10 nm

GaInAs emitter contact layers to minimize the emitter undercut etching. For fabrication details, see [1]. Fig. 7 shows a cross-section of a typical device (left) vs. our standard process. The base contact resistivity is  $\rho_{B,C} \approx 1 \ \Omega \cdot \mu m^2$ .

Fig. 8. Plot of  $f_T/f_{MAX}$  vs. collector current for various emitter mesa sizes with an E/B access distance of 35 nm. Several emitter sizes achieve  $f_{MAX} > 1$  THz, including an emitter mesa length of 9.4  $\mu$ m with  $A_E = 1.645 \ \mu m^2$  [1].

Fig. 9. Survey of reported InP DHBT metrics. Breakdown voltages are color-coded [1].

TABLE | COMPARATIVE ASSESSMENT OF STATE-OF-THE-ART SIGE HBT, TYPE-I AND TYPE-II INP DHBTS

|                                                        | SiGe HBT<br>[34] | Type-I:<br>GaInAs<br>[12] | Type-II:<br>GaAsSb<br>[1] |

|--------------------------------------------------------|------------------|---------------------------|---------------------------|

| Peak f <sub>T</sub> (GHz)                              | 505              | 520                       | 475                       |

| Peak f <sub>MAX</sub> (THz)                            | 0.72             | 1.15                      | 1.20                      |

| Emitter Area (µm²)                                     | 8×(0.105×1.0)    | 0.13×2.0                  | 0.25×4.4                  |

| $BV_{CEO}(V)$                                          | 1.6              | 3.5                       | 5.4                       |

| $f_{\rm T} \times BV_{\rm CEO}  ({ m THz-V})$          | 0.81             | 1.82                      | 2.56                      |

| $f_{\text{MAX}} \times BV_{\text{CEO}} (\text{THz-V})$ | 1.15             | 4.03                      | 6.48                      |

| $V_{\rm CE}/I_{\rm C}~({ m V/mA})$                     | 1.14 / 28.90     | 1.6 / 6.90                | 1.0 / 10.06               |

| $P_{\rm D}/A_{\rm E}~({\rm mW}/\mu{\rm m}^2)$          | 42.31            | 42.46                     | 9.15                      |

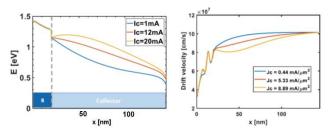

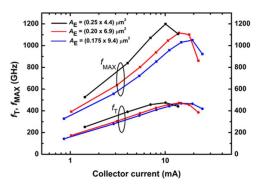

Fig. 8 summarizes the measured RF performance for various device geometries. Thanks to the low base metal resistance contribution, devices with an emitter length of 9.4  $\mu$ m achieve an unprecedented  $f_{\rm MAX} > 1$  THz—this is a clear breakthrough in THz DHBT scalability. Specifically,  $(0.20 \times 6.9)~\mu{\rm m}^2$  emitter devices show a peak  $f_{\rm MAX} = 1.10$  THz compared to 1.05 THz for  $(0.175 \times 9.4)~\mu{\rm m}^2$  DHBTs. As is usual with InP/GaAsSb DHBTs, high cutoff frequencies are accompanied by high  $BV_{\rm CEO}$  values: Fig. 9 puts our results in perspective with other InP DHBT technologies with color-coded breakdown voltages. Table I contrasts record  $f_{\rm T}/f_{\rm MAX}$

HBTs from the literature. Type-II DHBTs offer significantly higher  $f_{T,MAX} \times BV_{CEO}$  products. The dissipated power density in mW/ $\mu$ m<sup>2</sup> at the peak  $f_{MAX}$  bias point is also 4.6 times lower in InP/GaAsSb. Low power dissipation is advantageous in terms of efficiency, reduced self-heating and device reliability.

## B. THz DHBT 94 GHz Large-Signal Performance

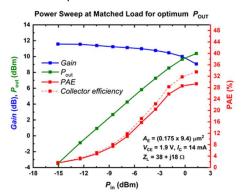

We performed single-tone continuous-wave CW power measurements at 94 GHz on single finger  $(0.175 \times 9.4) \, \mu \text{m}^2$  DHBTs biased for class-A operation. The source impedance was set to 50  $\Omega$ , and the load impedance was swept to determine the optimal load match for best saturation output power  $P_{\text{OUT,SAT}}$  and power added efficiency (PAE). The best efficiency and saturated output power were obtained at  $V_{\text{CE}} = 1.6$  and 1.9 V, respectively. These voltages are significantly higher than that yielding peak  $f_{\text{T}}/f_{\text{MAX}}$ . In all cases, the collector current density was  $\sim 8.5 \, \text{mA}/\mu \text{m}^2$  at low- $P_{\text{in}}$ .

Fig. 10. 94 GHz single-tone CW power characteristics of a (0.175  $\times$  9.4)  $\mu$ m<sup>2</sup> DHBT biased and matched for peak output power. [1].

Fig. 11. 94 Top: GHz load-pull contours of a  $(0.3 \times 9) \, \mu\text{m}^2$  common-emitter single finger DHBT for optimum  $P_{\text{OUT}}$  (left) and optimum gain (right). Bottom: Ultra-wideband single-stage amplifier implemented with the same DHBTs.

When biased for efficiency an excellent PAE = 32.5% is obtained with simultaneous  $P_{\text{OUT,SAT}} = 8.73$  dBm and a gain of 7.8 dB at 94 GHz. The collector efficiency is 40.3%, and the linear gain of the device at this bias is 11.85 dB. The peak

saturated output power at  $V_{\rm CE}=1.9~{\rm V}$  and  $V_{\rm BE}=832~{\rm mV}$  is  $10.4~{\rm dBm}$  with a corresponding gain of  $9.1~{\rm dB}$  and PAE=29.3%, as shown in Fig. 10. This corresponds to a power density of  $6.67~{\rm mW/\mu m^2}$  ( $1.17~{\rm W/mm}$ ). The optimum load impedances  $Z_{\rm L}$  for peak efficiency and maximum output power are quite similar, indicating excellent device versatility. It is noteworthy that the  $V_{\rm CE}$  biases used in these large-signal measurements far exceed the  $V_{\rm CE}=1.0~{\rm V}$  required for peak small-signal performance: our  $0.175~{\rm \mu m}$  wide devices with peak  $f_{\rm MAX}=1.05~{\rm THz}$  operate stably, with no evidence of degradation. Such device stability under aggressive large-signal operation suggests inherent reliability advantages in the InP-GaAsSb material system. No thermal management techniques (e.g. heatsinking or substrate thinning/transfer) were used: better performances can be expected with their application.

## C. Sub-THz DHBT Large-Signal Performance at 94 GHz

The use of fine emitter widths to maximize  $f_{\text{MAX}}$  necessarily reduces the emitter area for a given emitter length: this limits the maximum deliverable output power per single emitter. For mm- and sub-mm-wave applications, the performance of wider emitter devices should also be investigated.

We characterized Type-II  $(0.3 \times 9) \mu m^2$  DHBTs realized in the standard (non-fin) ETHZ-MWE process. Load-pull measurements were carried out for single-finger commonemitter (0.3×9)  $\mu$ m<sup>2</sup> DHBTs in class-A bias. Contours for  $P_{OUT}$ at 3-dB-back-off input power are depicted in Fig. 11. The optimum load for maximum  $P_{\text{OUT}}$  is  $Z_{\text{L}} = (31.8 - j17) \Omega$ . The domains of high output power extend close to the center of the Smith chart, and there is a good overlap with optimum gain impedances. As a demonstrator, a single-stage 60-160 GHz amplifier was fabricated. The small-signal RF amplifier gain is > 7 dB up to 110 GHz, and > 7 dB to 160 GHz (Fig. 11, bottom). It delivers 8 dBm large-signal  $P_{OUT}$  at 94 GHz with a DC power consumption of only 34 mW. In other still unpublished work, a maximum saturation output power  $P_{OUT,SAT} = 14.5 \text{ dBm}$  and a 10.4 mW/μm<sup>2</sup> power density at 94 GHz were achieved for devices of similar size, a record for InP DHBTs measured at Wband (without thermal management techniques).

# IV. FROM INP DHBT TECHNOLOGY TO HIGH-SYMBOL-RATE AND LARGE-OUTPUT SWING INTEGRATED CIRCUITS

Advances in optical/electronic (O/E) technologies and in communication systems using new transmission formats allow higher transmission rates with increased spectral efficiency. Multi-level coded transmission, and in particular the four-level pulse-amplitude modulation (PAM-4) format, are widely used in optical communications. High-symbol-rate and large-swing drivers are key electronic components empowering modern high-capacity transmitters.

Indeed, to efficiently drive the electro-optical modulators that modulate the optical carrier, linear drivers must combine a wide output swing with a high gain-bandwidth product and a low power consumption. Such requirements are hence very demanding in terms of transistor performance: they must combine very high  $f_{\rm T}/f_{\rm MAX}$ , a wide safe operating area, and a

high  $BV_{\text{CEO}}$ , while maintaining a high transconductance and performance stability under high thermal stress. InP/GaAsSb DHBTs provide a low turn-on voltage, a high current gain  $\beta$ , a low  $C_{\text{BC}}$ , and high cutoff frequencies with a high  $BV_{\text{CEO}}$  [1]: this combination makes them particularly interesting for very-high symbol-rate IC design.

## A. InP/GaAsSb Epitaxy and III-V Lab 0.7-µm DHBT Process

Fig. 12. SEM microphotograph of a  $0.7\times5~\mu\text{m}^2$  InP/GaAsSb DHBT.

The InP/GaAsSb DHBT structure was grown by metal organic vapor-phase epitaxy (MOVPE) on a 3-inch semi-insulating InP substrate at ETH-Zurich. The emitter cap layer includes a  $5\times10^{19}$ -cm<sup>-3</sup> Si-doped In-rich InGaAs layer to minimize the emitter contact resistivity. Type-II DHBT emitter structure uses a composite 40-nm thick InP/GaInP emitter. A compositionally graded GaAs<sub>x</sub>Sb<sub>1-x</sub> base (with x=0.6 on emitter side and x=0.4 on collector side) reduces the base transit time. A base average C-doping of  $8\times10^{19}$  cm<sup>-3</sup> keeps its sheet resistance low. The low-doped GaInP emitter reduces the Type-II  $\Delta E_{\rm C}$  at the E/B interface, and increases the current gain, as previously stated. The collector is a 130-nm-thick  $2.5\times10^{16}$ -cm<sup>-3</sup> Si-doped InP layer, allowing a full collector depletion at low bias. The B/C layers resemble those of the THz DHBTs of Section III.A, illustrates the B/C design versatility.

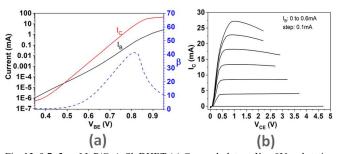

Fig. 13.  $0.7 \times 5 \ \mu\text{m}^2$  InP/GaAsSb DHBT (a) Gummel plots at  $V_{\text{BC}}\!\!=\!\!0\text{V}$  and static current gain as a function of base-emitter voltage. (b)  $I_{\text{C}}\!\!-\!V_{\text{CE}}$  characteristics.

Type-II DHBTs were fabricated at III-V Lab using weterching and a self-aligned triple mesa technology. The process is similar to that commonly used to realize InP/GaInAs DHBTs [23]. Transistors have a hexagonal shape with a 0.7-µm emitter width and 5-, 7- and 10-µm emitter lengths. TLM measurements reveal an emitter contact resistivity of 4  $\Omega$ .µm², a base sheet resistance as low as 790  $\Omega$ / $\square$ , and a base contact resistivity of ~30  $\Omega$ .µm². The latter is 10× higher than obtained on GaInAs base of similar C-doping level at III-V Lab. As the Fermi level pins is closer to the valence band on GaAsSb than on GaInAs, further optimization of the base process is likely. Fig. 12 shows a scanning electron microscopy (SEM) view of the 0.7×5 µm² transistor before interconnect. Additional circuit

fabrication steps include NiCr thin film resistors, SiN MIM capacitors and three Au-based interconnection levels.

## B. Device Performance

Gummel plots at a 0-V  $V_{BC}$ , and the DC gain, for a typical  $0.7 \times 5 - \mu m^2$  DHBT, are depicted in Fig. 13(a). The GaAsSb-based DHBT exhibits a peak DC gain of 42 at  $V_{BE} = 0.8$  V. The base and collector ideality factors are 1.72 and 1.0, respectively.

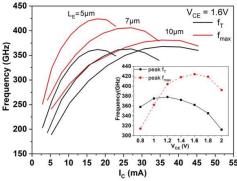

Fig. 14.  $f_T$  and  $f_{MAX}$  versus collector current for 0.7- $\mu$ m InP/GaAsSb DHBTs with three different emitter lengths. The inset shows peak  $f_T$  and  $f_{MAX}$  as a function of emitter-collector voltage for a  $0.7\times5-\mu$ m² device.

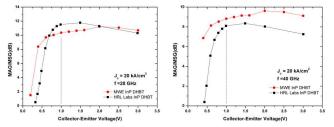

Fig. 13(b) shows 0.7×5-μm<sup>2</sup> transistor output characteristics. 70-mV emitter-collector offset voltage is obtained as well as 0.5-V knee voltage, at a 6-mA/ $\mu$ m<sup>2</sup> collector current ( $J_C$ ). The common emitter-collector breakdown voltage ( $BV_{CEO}$ ) is 4.7 V at  $J_{\rm C} = 30 - \mu {\rm A}/\mu {\rm m}^2$  with a large safe operating area. Transistor's negative output conductance, observed at high currents, indicates that self-heating occurs. The extracted thermal resistance at a 25-mW power ( $I_C = 15 \text{ mA}$  and  $V_{CE} = 1.65 \text{ V}$ ) is 4.7 K/mW. Fig. 14 depicts  $f_T$  and  $f_{MAX}$  versus collector current for representative 0.7-µm devices, with different emitter lengths, at  $V_{\text{CE}} = 1.6 \text{ V}$ . The peak  $f_{\text{T}}$  and  $f_{\text{MAX}}$  for  $0.7 \times 5 - \mu \text{m}^2$  DHBTs at  $J_{\rm C} \sim 6~{\rm mA/\mu m^2}$  exceed 360 and 420 GHz, respectively.  $f_{\rm T}$ slightly increases with emitter length whereas  $f_{MAX}$  decreases because the extrinsic base resistance does not scale inversely with emitter length. The Fig. 14 inset illustrates the peak frequency performance dependence on  $V_{\rm CE}$  for a  $0.7\times5$ - $\mu{\rm m}^2$ InP/GaAsSb DHBT, clearly showing higher  $f_T$  at lower  $V_{CE}$ (peak  $f_T \sim 380$  GHz at  $V_{CE} = 1.2$  V). The curves highlight the advantage of Type-II DHBTs in maintaining a high performance at low bias ( $V_{CE} < 1.2 \text{ V}$ ): in contrast to GaInAs-based DHBTs, no collector current blocking occurs when the B/C is slightly reverse biased. As shown below, this InP/GaAsSb DHBT technology is very well-suited to combined high symbol-rate and large output swing circuit applications.

## C. InP/GaAsSb/InP-DHBT Lumped Linear Driver

## 1) Linear Driver Design

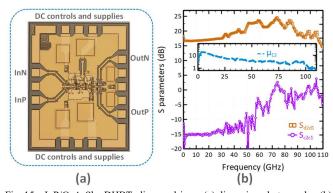

The lumped linear driver was designed and fabricated at III-V Lab around the 0.7-μm InP/GaAsSb DHBTs described in Section IV.A. A die microphotograph is shown in Fig. 15. The driver dimensions are 1.2×1.5 mm² and its active core region is 0.6×0.2 mm². The linear driver was designed using an electromagnetic-circuit co-simulation design flow [24].

The driver has a three-stage differential-amplifying-cell architecture, and is composed of a pre-amplifier and a largeswing linear output stage. The pre-amplifier provides input impedance matching on a 100- $\Omega_{\text{diff}}$  source, differential gain, equalization capabilities and common-mode rejection to ensure good differential operation. Its amplifying cells consist of emitter followers and a resistively-degenerated differential pair to ensure linear operation. An additional emitter follower stage is interposed between the pre-amplifier and the output stage to ensure impedance matching and minimize bandwidth degradations. The output stage relies on a paralleled-transistor cascode differential architecture with emitter resistive degeneration [25], to combine a large linear output swing and a high gain-bandwidth product. Inductive peaking was implemented to further increase the driver equalization capabilities, as well as the overall bandwidth and the output impedance matching on a 100- $\Omega_{\text{diff}}$  load.

Fig. 15. InP/GaAsSb DHBT linear driver (a) die microphotograph. (b) Measured differential- and common-mode S-parameter gains. Inset:  $\mu$  stability factor.

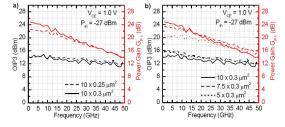

# 2) Linear Driver Characterisation and Performance

The linear driver S-parameter on-wafer measurements were conducted from 70 kHz to 110 GHz. Fig. 15(b), depicts the linear driver differential- and common-mode gains, as well as the  $\mu$  stability factor, which have been retrieved from the singleended S-parameter measurements (Fig. 15(b) inset). At 40 MHz, the differential gain,  $|S_{d2d1}|$ , is 16.7 dB, while the driver shows a beyond-110-GHz -3-dB-bandwidth, exceeding the vector network analyzer frequency range. This results in a gain-bandwidth product in excess of 752 GHz. This linear driver also shows high equalization capabilities with up to 7.9dB of equalization gain at 74 GHz. Besides, as shown on Fig. 15(b), at low frequencies, a -15-dB common-mode gain,  $|S_{c2c1}|$ , is obtained, yielding a 31-dB common-mode rejection ratio (CMRR). The CMRR remains above 17 dB across 110 GHz, thus ensuring good differential operation across the entire driver bandwidth. Additionally, the lumped linear driver remains unconditionally stable up to 108 GHz ( $\mu > 1$ ), thanks to a good impedance matching to the 100- $\Omega_{\rm diff}$  source and load, and a low reverse gain (less than -30 dB across 110 GHz). Therefore, Type-II DHBTs offer some of the highest gainbandwidth product and equalization capabilities when compared to the linear driver state-of-the-art, see [24-29].

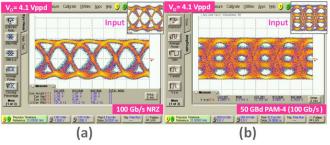

Lumped linear driver on-wafer large-signal digital measurements were performed at 100 Gb/s, both with four-level pulse-amplitude modulation (PAM-4) and non-return-to-zero (NRZ) modulations. The Fig. 16(a) inset shows the (2<sup>15</sup>–1)-bit 50-Gb/s PRBS input signals. Fig. 16(a) depicts the linear driver 4.1-Vppd 100-Gb/s NRZ output signal eye diagram with clear eye opening. This emphasizes the InP/GaAsSb-DHBT linear driver's ability to combine a large-output swing with high-symbol-rate operation, while ensuring a high signal integrity. Indeed, a 3-V differential eye amplitude is obtained, while the eye signal-to-noise ratio (S/N) is 7 and the rms-jitter remains below 730 fs. To the best of the authors' knowledge, this constitutes the highest >3-Vppd 100-Gb/s NRZ eye S/N reported for a linear driver to date.

Fig. 16(b) shows the linear driver 4.1-Vppd 50-GBd PAM-4 output eye diagram with a driver power consumption of 0.85-W. The DAC input signals are depicted in the Fig. 16(b) inset, where strong setup limitations can be observed, thus limiting the driver output signal quality. During PAM-4 measurements, the DAC output stage currents were scaled to exceed the driver 1-dB compression point. Note that no digital signal processing (DSP) or post-processing were used in driver measurements. Additionally, a significant fraction of the driver equalization capabilities was absorbed to compensate for the setup bandwidth limitations.

Fig. 16. InP/GaAsSb DHBT linear diver large-signal digital measurements (a) 100-Gb/s NRZ differential eye diagram. Horizontal and vertical scales are respectively 5 ps/div and 1 V/div. Inset: differential input signal. (b) 50-GBd PAM-4 differential eye diagram. Horizontal and vertical scales are respectively 10 ps/div and 1 V/div. Inset: differential input signal.

## D. InP/GaAsSb/InP DHBT 2-bit DAC-Driver

One of the key architectures allowing for the combination of high-speed and high-swing is the power-DAC [30]. The power-DAC circuit was the basis of the first single-carrier 1.0 Tb/s transmitter [31].

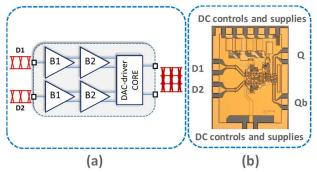

The presented DAC-driver circuit [32] transforms 2 binary input data streams into an amplified PAM-4 differential output signal. This DAC-driver block diagram is shown in Fig. (a). Two NRZ input signals (LSB and MSB) are first converted from single-ended (SE) to differential ones (B1) and amplified (B2). The resulting signals are combined and amplified to obtain differential PAM-4 output signals. Specific control functionalities are also provided to optimize the E/O response of the combined driver and modulator. These functionalities are: output driving swing adjustment, static predistortion to compensate for the E/O characteristic nonlinearity, pre-

compensating modulator's limited bandwidth and providing necessary DC offset.

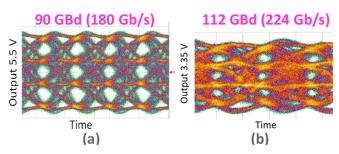

Fig. 17. InP/GaAsSb DHBT DAC-driver (a) circuit block diagram. (b) die microphotograph.

Fig. 18. InP/GaAsSb DHBT DAC-driver PAM-4 measurements. (a) 90-GBaud (180 Gb/s) PAM-4 5.5-Vppd output-swing differential eye diagram. Scale: (1V/div, 5ps/div). (b) 112-GBaud (224 Gb/s) PAM-4 3.35-Vppd output-swing differential eye diagram. Scale: (1V/div, 5ps/div).

Both electrical simulation and circuit layout obey high frequency design rules. A compact layout is privileged to maximally shorten signal interconnections. However, the output cascode block is a critical region, where thermal dissipation needs to be correctly addressed. The power density is high, and a proper trade-off between signal integrity and safe heat dissipation needs to be found.

The InP/GaAsSb DHBT IC shown in Fig. 17(b), was implemented in the III-V Lab 0.7- $\mu$ m technology described in Section IV.A. It is composed of 37 transistors and its footprint is 1.2×1.5 mm², while the circuit's core dimensions are 520×470  $\mu$ m². The DHBTs were operated at  $J_C = 5$ -6 mA/ $\mu$ m².

PAM-4 measurements of the DAC-driver at 90 GBd (180 Gb/s) and 112 GBd (224 Gb/s) are presented in Fig. 18. The power consumption is 1.1 and 0.6-W for the two respective symbol-rates. It should be noted that our measurements include cables, transitions, delay lines and DC blocks, all of which impact signal integrity. The 90-GBd PAM-4 differential output eye diagram with a record 5.5-Vppd swing and an excellent eye quality is presented in Fig. 18(a). A gain control capability of over 12-dB was also obtained. The circuit measurements at 112 GBd in PAM-4 is presented in Fig. 18(b), also with a record 3.35-Vppd output swing. It should be noted that the 112 Gb/s measurement input interface has a significant negative impact on the input signal quality. The E/O driver figure-of-merit (FoM) in terms of the PAM-4 symbol-rate  $D_{\rm S}$ , the differential output swing  $V_{\text{Opp}}$ , the differential output matching impedance  $Z_0$ , and the circuit's DC power consumption  $P_{DC}$  is

$$FoM = D_{\rm S}V_{\rm Opp}^2/8Z_0P_{\rm DC},$$

leading to record FoM values of 3.1 and 2.6 GBd at 180 and 224 Gb/s, respectively. They are to be compared to the E/O FoM of 0.13 GBd achieved in a 256 Gbs PAM-4 generator IC implemented around 0.25- $\mu$ m InP/GaInAs DHBTs with  $f_T/f_{\rm MAX} = 460/480$  GHz ( $J_{\rm C} = 10$ -13 mA/ $\mu$ m²) [33]. Our data demonstrate the outstanding properties of InP/GaAsSb DHBTs for high symbol-rate large output swing mixed-signal ICs: a favorable band structure is key —raw transistor metrics (*i.e.* high peak  $f_T/f_{\rm MAX}$  and  $J_{\rm C}$ ) are *not* sole determinants of mixed-signal IC performance. A high performance over wide signal swings is a strong advantage of "Type-II" DHBTs technology.

### ACKNOWLEDGMENT

The work at III-V Lab was also supported by the Photonics Public Private Partnership Initiatives' QAMeleon (N°780354) and TWILIGHT EU (N°871741) projects.

#### REFERENCES

- [1] A. M. Arabhavi *et al.*, "InP/GaAsSb Double Heterojunction Bipolar Transistor Emitter-Fin Technology with  $f_{\text{MAX}} = 1.2 \text{ THz}$ ," in IEEE Trans. on Electron Devices, vol. 69, no. 4, pp. 2122-2129, 2022. doi: 10.1109/TED.2021.3138379.

- [2] Y. Shiratori *et al.*, "InGaP/GaAsSb/InGaAsSb/InP Double Heterojunction Bipolar Transistors with Record  $f_{\rm T}$  of 813 GHz," in IEEE Electron Device Letters, vol. 41, no. 5, pp. 697-700, 2020. doi: 10.1109/LED.2020.2982497.

- [3] NSERC Awards Database: <a href="https://www.nserc-crsng.gc.ca/ase-oro/Details-Detailles\_eng.asp?id=1273">https://www.nserc-crsng.gc.ca/ase-oro/Details-Detailles\_eng.asp?id=1273</a>

- [4] J. Hu et al., "Type II photoluminescence and conduction band offsets of GaAsSb/InGaAs and GaAsSb/InP heterostructures grown by metalorganic vapor phase epitaxy," Appl. Phys. Lett. 73, pp. 2799-2801 1998. doi: 10.1063/1.122594

- [5] The SRC Decadal Plan for Semiconductors, Full Report, p.24.

- [6] B. T. McDermott et al., "Growth and doping of GaAsSb via metalorganic chemical vapor deposition for InP heterojunction bipolar transistors, Appl. Phys. Lett. 68, pp. 1386-1388, 1996. Doi: 10.1063/1.116088

- [7] X. G. Xu et al. "Metalorganic vapor phase epitaxy of high-quality GaAs<sub>0.5</sub>Sb<sub>0.5</sub> and its application to heterostructure bipolar transistors," Appl. Phys. Lett. 74, pp. 976-978, 1999. doi:10.1063/1.123428.

- [8] R. Bhat et al., "InP/GaAsSb/InP and InP/GaAsSb/InGaAsP double heterojunction bipolar transistors with a carbon-doped base grown by organometallic chemical vapor deposition," Appl. Phys. Lett. 68, pp. 985-987, 1996. doi: 10.1063/1.116120.

- [9] N. Matine et al., "Demonstration of GSMBE grown InP-GaAs<sub>0.51</sub>As<sub>0.49</sub> /InP DHBTs," Conference Proceedings. 2000 International Conference on Indium Phosphide and Related Materials, 2000, pp. 239-242, doi: 10.1109/ICIPRM.2000.850276.

- [10] H.G Liu et al., "High-performance InP/GaAsSb/InP DHBTs grown by MOCVD on 100mm InP substrates using PH<sub>3</sub> and AsH<sub>3</sub>," J. of Crystal Growth 267, pp. 592-597, 2004. doi: 10.1016/j.jcrysgro.2004.04.035.

- [11] T.S. Low, Personal communication.

- [12] M. Urteaga et al., "130nm InP DHBTs with ft >0.52THz and fmax >1.1 THz," 69th Device Research Conference IEEE, June 2011, pp. 281-282, doi: 10.1109/DRC.2011.5994532.

- [13] Y. Tang *et al.*, "Ultrahigh-Speed GaN High-Electron-Mobility Transistors with  $f_T/f_{MAX}$  of 454/444 GHz," IEEE Electron Dev. Lett., vol. 36, no. 6, pp. 549-551, 2015. doi: 10.1109/LED.2015.2421311.

- [14] X. Mei et al., "First Demonstration of Amplification at 1 THz Using 25-nm InP High Electron Mobility Transistor Process," IEEE Electron Dev. Lett., vol. 36, no. 4, pp. 327-329, 2015. doi: 10.1109/LED.2015.2407193.

- [15] T. Shivan et al., "A Highly Efficient Ultrawideband Traveling-Wave Amplifier in InP DHBT Technology," in IEEE Microwave and Wireless

- Comp. Lett., vol. 28, no. 11, pp. 1029-1031, 2018. doi: 10.1109/LMWC.2018.2871336.

- [16] M. Hossain *et al.*, "A 0.5 THz Signal Source with –11 dBm Peak Output Power Based on InP DHBT, *2019 49th European Microwave Conference (EuMC)*, 2019, pp. 856-859. doi: 10.23919/EuMC.2019.8910876.

- [17] P.-F. Chen et al., "Application of GaInP/GaAs DHBTs to power amplifiers for wireless communications," in IEEE Trans. on Microwave Theory and Techniques, vol. 47, no. 8, pp. 1433-1438, Aug. 1999, doi: 10.1109/22.780391.

- [18] P. J. Zampardi et al., "Suitability of InP DHBTs in ET/APT Systems," 2016 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), 2016, pp. 1-4, doi: 10.1109/CSICS.2016.7751067.

- [19] K. Y. Cheng et al., "Base charge accumulation and push-out effects on nonlinearity of Type-I InP/InGaAs/InP and Type-I/II AlInP/GaAsSb/InP double heterojunction bipolar transistors," J. of Appl. Phys. 110, 113703, 2011. doi: 10.1063/1.3662152.

- [20] C. R. Bolognesi et al., "III-V GaAs and InP HBT devices for 4G & 5G wireless applications," 2018 China Semicond. Technology International Conference (CSTIC), 2018, pp. 1-4, doi: 10.1109/CSTIC.2018.8369168.

- [21] P. Sakalas et al., "Harmonic distortion analysis of InP HBTs with 650 GHz fmax for high data rate communication systems," 2017 IEEE Compound Semicond. Int. Circuit Symp. (CSICS), 2017, pp. 1-4, doi: 10.1109/CSICS.2017.8240429.

- [22] X. Wen et al., "A multiscale TCAD approach for the simulation of InP DHBTs and the extraction of their transit times," IEEE. Trans. Electron Devices 66, pp. 5084-5090 (2019). doi: 10.1109/TED.2019.2946514.

- [23] V. Nodjiadjim *et al.*, "0.7- $\mu$ m InP DHBT technology with 400-GHz  $f_T$  and  $f_{MAX}$  and 4.5-V  $BV_{CEO}$  for high speed and high frequency integrated circuits," IEEE J. of the Electron Devices Soc., pp. 748–752, 2019. doi: 10.1109/JEDS.2019.2928271

- [24] R. Hersent et al., "Design, modelling and characterization of a 3-Vppd 90-GBaud over-110-GHz-bandwidth linear driver in 0.5-μm InP DHBTs for optical communications," 2021 BCICT Symp. Proc., Monterey, CA, USA, 2021. doi: 10.1109/BCICTS50416.2021.9682463.

- [25] R. Hersent et al., "Over 70-GHz 4.9-Vppdiff InP linear driver for next generation coherent optical communications," 2019 IEEE BCICT Symposium, 2019. doi: 10.1109/BCICTS45179.2019.8972779.

- [26] R. Hersent et al., "106-GHz bandwidth InP DHBT linear driver with a 3-Vppdiff swing at 80 GBd in PAM-4," Electronics Letters 56, pp. 691-693, 2020. doi:10.1049/el.2020.0654.

- [27] A. Zandieh et al., "57.5-GHz bandwidth 4.8 Vpp swing linear modulator driver for 64 GBd m-PAM systems," 2017 IEEE MTT-S Int. Microwave Symposium (IMS), 2017. doi: 10.1109/MWSYM.2017.8058847.

- [28] M. Nagatani, et al., "A 3-Vpp 730-mW linear driver IC using InP HBTs for advanced optical modulations," IEEE Comp. Semicond. Int. Circuits Symp. (CSICS), Oct. 2013. doi: 10.1109/CSICS.2013.6659193.

- [29] H. Abdelrahman et al., "A 6V swing 3.6% THD >40GHz driver with 4.5× bandwidth extension for a 272 Gb/s dual-polarization 16-QAM silicon photonic transmitter," 2019 IEEE ISSC Proc., 2019. doi: 10.1109/ISSCC.2019.8662318.

- [30] A. Konczykowska et al., "Extreme speed power-DAC: Leveraging InP DHBT for ultimate capacity single-carrier optical transmissions," J. of Lightwave Tech., vol. 36, no. 2, pp. 401-407, 2018. doi: 10.1109/JLT.2017.2760507.

- [31] G. Raybon, et al. "Single carrier high symbol rate transmitter for data rates up to 1.0 Tb/s," Optical Fiber Communication Conference. Optical Society of America, 2016.

- [32] A. Konczykowska et al., "112 GBaud (224 Gb/s) large output swing InP DHBT PAM-4 DAC-driver", 24<sup>th</sup> International Microwave and Radar Conference MIKON'22, Gdansk, Sept 2022.

- [33] M. Nagatani et al., "A 256-Gbps PAM-4 Signal Generator IC in 0.25-μm InP DHBT Technology," 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2018, pp. 28-31. doi: 10.1109/BCICTS.2018.8550977.

- [34] B. Heinemann et al., "SiGe HBT with fx/fmax of 505 GHz/720 GHz," 2016 IEEE Int. Electron Dev. Meeting (IEDM), 2016, pp. 3.1.1-3.1.4, doi: 10.1109/IEDM.2016.7838335.